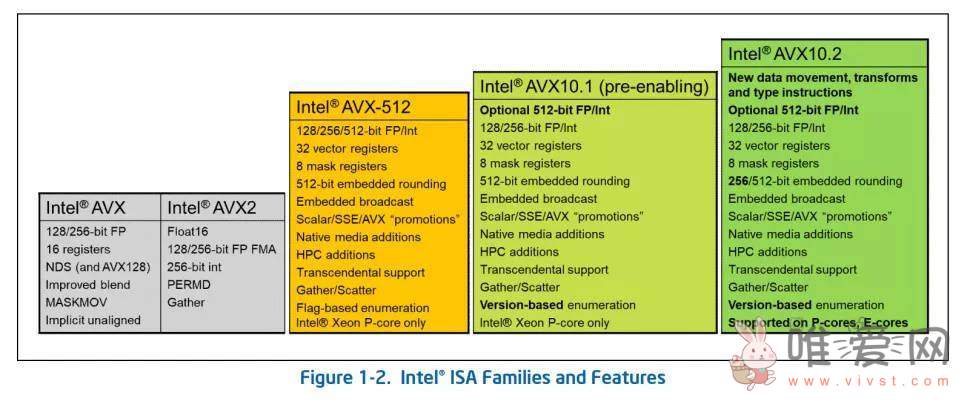

英特尔今日发布了全新的高级性能扩展指令集 (APX),并介绍了即将为 P 核和 E 核提供统一 AVX-512 支持的新型 AVX10 指令集。简单来说,AV10(Advanced Instruction Extensions 10) ISA 是 AVX-512 的超集,并具有 256bit 和 512bit 寄存器大小的所有 AVX-512 ISA 功能。

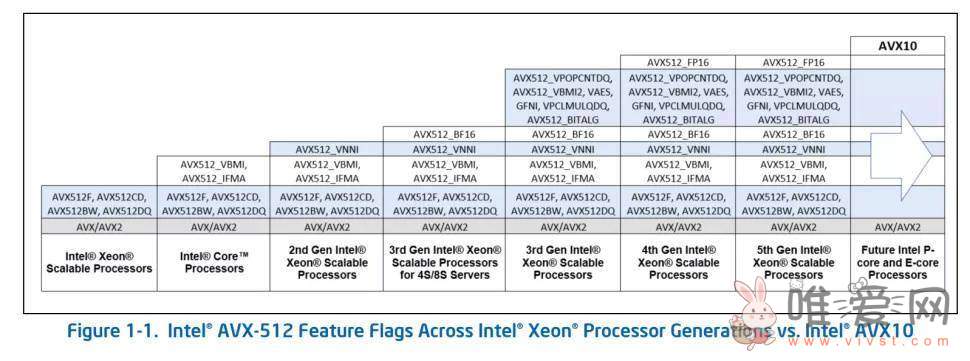

这种新的指令集暂时没有英特尔 CPU 支持 —— 它预计将在未来的芯片中出现,初代便是“Granite Rapids”。英特尔表示,AVX10 将成为其面向未来消费者和服务器处理器的矢量 ISA 选择。

英特尔今日发布全新的高级性能扩展指令集:暂时没有英特尔CPU支持!

从最基本的层面来看,AVX10 将使同时具有 E 核和 P 核的英特尔芯片支持 AVX-512,尽管 512bit 版本只能在 P 核上运行,不过 256bit 的 AVX-256 模拟指令集可以同时在 P 核和 E 核上运行。

据介绍,AVX10 将包括“带有 AVX512VL 功能标志的 AVX-512 矢量指令、最大矢量寄存器长度为 256bit 以及八个 32bit 掩码寄存器,以及支持嵌入式舍入的新 256bit 指令”。

这个版本可以在 P 核和 E 核上运行,但 E 核限制为最大 256bit 长度,而 P 核可以使用完整的 512bit 矢量,这一点类似于 Arm 通过 SVE 对可变矢量宽度的支持。

英特尔表示,现有应用程序在 AVX10 上的性能与 AVX-512 相同,至少在相同的矢量长度上。英特尔还声称:英特尔 AVX2 编译的应用程序重新编译为 AVX10 后无需额外软件调整即可实现性能提升。

得益于新增的 16 个矢量寄存器和新指令,对于矢量寄存器压力敏感的英特尔 AVX2 应用程序可获得大幅性能提升。高度线程化的可矢量化应用程序在使用基于 Intel Xeon E 内核的处理器或具有混合架构的 Intel 产品时,可能实现更高的总吞吐量。

英特尔今日发布全新的高级性能扩展指令集:暂时没有英特尔CPU支持!

后续,英特尔将为消费级客户提供 Meteor Lake,为 HPC 客户提供 Granite Rapids 和 Sierra Forest,而这三个系列均采用类似的架构,其 P 核为 Redwood Cove 核,E 核则基于 Crestmont 架构。

据悉,英特尔将从第六代 Xeon“Granite Rapids”芯片开始支持 AVX10 首个版本(AVX10.1),但该版本只支持 512bit 矢量指令,而不是新的 256bit 矢量指令。也就是说,这一代只是作为从 AVX-512 到 AVX10 的过渡芯片。不过,未来所有的 Xeon 处理器本身就会继续支持完整的 AVX-512 指令,以确保传统应用正常运行。

英特尔今日发布全新的高级性能扩展指令集:暂时没有英特尔CPU支持!

后续的 AVX10.2 将支持 256bit 矢量长度和其他新功能,如新的 AI 数据类型和转换、数据移动优化和标准支持。为了解决开发者的担忧,英特尔还计划为 AVX10 实现与 AVX-512 相比大大简化的枚举方式,并确保每次转向新修订版时都有足够的新指令和功能值得升级变,从而减少版本和枚举膨胀。

声明:本文内容采编自互联网,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容,请点击举报,一经查实,本站将立刻删除。